Enunciado

Añadir al biestable del ejercicio anterior una entrada de reloj activa a nivel alto:

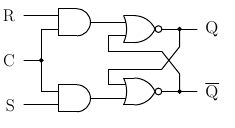

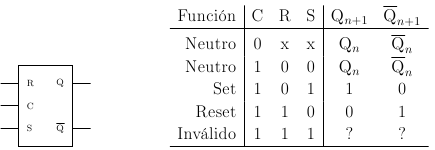

Primera solución

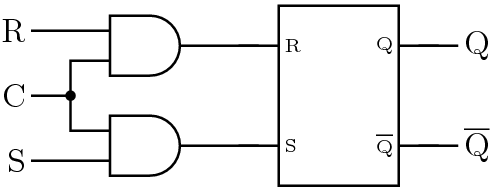

Vamos a solucionar el problema basándonos en el módulo RS construido en el ejercicio anterior. Usando uno de esos módulos, el problema nos queda según el siguiente esquema:

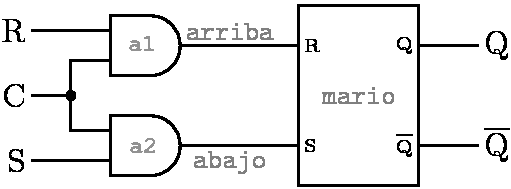

Procedemos a dar nombre a las puertas y a los cables que no lo tengan:

Construimos el módulo:

/* MOdulo RS copiado del ejercicio anterior */ module RS (output wire Q, output wire nQ, input wire R, input wire S); nor n1(Q, R, nQ); nor n2(nQ, S, Q); endmodule /* MOdulo RSC basado en el mOdulo RS anterior */ module RSC (output wire Q, output wire nQ, input wire R, input wire C, input wire S); wire arriba; wire abajo; and a1 (abajo, R, C); and a2 (abajo, C, S); RS mario (Q, nQ, arriba, abajo); endmodulePor un procedimiento similar, construimos un módulo de prueba con un módulo RSC, varios registros y cables para probarlo, y una orden

$monitor para que haga el seguimiento de las

señales. Puede quedar algo como esto:

module test;

reg david;

reg victor;

reg silvia;

wire alvaro;

RSC adrian(alvaro, ,david,silvia,victor);

initial

begin

$monitor($time," C=%b, R=%b, S=%b, Q=%b", silvia, david, victor, alvaro);

david=0; victor=0; silvia=1;

#5 david=0; victor=1;

#5 david=0; victor=0;

#5 david=1; victor=0;

#5 david=1; victor=1;

#5 david=0; victor=0;

#5 david=1; victor=1;

#5 victor=0; david=0;

#5 david=0; victor=1; silvia=0;

#5 david=0; victor=0;

#5 david=1; victor=0;

#5 david=1; victor=1;

#5 david=0; victor=0;

#5 david=1; victor=1;

#5 victor=0; david=0;

#5 victor=0; david=0;

end

endmodule

El registro silvia da cuenta de la señal de reloj.

Cuando este registro valga 0, el biestable es inmune a las señales

R y S. Comprobémoslo ejecutándolo:

0 C=1, R=0, S=0, Q=x

5 C=1, R=0, S=1, Q=x

10 C=1, R=0, S=0, Q=x

15 C=1, R=1, S=0, Q=x

20 C=1, R=1, S=1, Q=x

25 C=1, R=0, S=0, Q=x

30 C=1, R=1, S=1, Q=x

35 C=1, R=0, S=0, Q=x

40 C=0, R=0, S=1, Q=x

45 C=0, R=0, S=0, Q=x

50 C=0, R=1, S=0, Q=x

55 C=0, R=1, S=1, Q=x

60 C=0, R=0, S=0, Q=x

65 C=0, R=1, S=1, Q=x

70 C=0, R=0, S=0, Q=x

¡Ups! Parece que ha habido un error...

Depuración

El error parece que se produce en la salida Q. Las señales que no controlamos y que pueden ser fuente del error son los cables internosarriba y abajo del módulo

RSC, que hemos llamado adrian. Pues le decimos

a $monitor que haga un seguimiento de esas señales

también:

$monitor($time," C=%b, R=%b, S=%b, arriba=%b, abajo=%b, Q=%b", silvia,

david, victor, adrian.arriba, adrian.abajo, alvaro);

Observad cómo usamos el operador punto (.) para

acceder al interior de adrian. Si ejecutamos, aparece:

0 C=1, R=0, S=0, arriba=z, abajo=0, Q=x

5 C=1, R=0, S=1, arriba=z, abajo=x, Q=x

10 C=1, R=0, S=0, arriba=z, abajo=0, Q=x

15 C=1, R=1, S=0, arriba=z, abajo=x, Q=x

20 C=1, R=1, S=1, arriba=z, abajo=1, Q=x

25 C=1, R=0, S=0, arriba=z, abajo=0, Q=x

30 C=1, R=1, S=1, arriba=z, abajo=1, Q=x

35 C=1, R=0, S=0, arriba=z, abajo=0, Q=x

40 C=0, R=0, S=1, arriba=z, abajo=0, Q=x

45 C=0, R=0, S=0, arriba=z, abajo=0, Q=x

50 C=0, R=1, S=0, arriba=z, abajo=0, Q=x

55 C=0, R=1, S=1, arriba=z, abajo=0, Q=x

60 C=0, R=0, S=0, arriba=z, abajo=0, Q=x

65 C=0, R=1, S=1, arriba=z, abajo=0, Q=x

70 C=0, R=0, S=0, arriba=z, abajo=0, Q=x

Se observa que el cable arriba parece estar dando

problemas. Si revisamos el módulo RSC, veremos

que es que nos habíamos equivocado justo ahí, en la

conexión de la puerta a1, que debe decir:

and a1 (arriba, R, C);Si ejecutamos ahora el módulo, el resultado ya es el correcto: cuando el reloj es cero, R y S no afectan al biestable.

0 C=1, R=0, S=0, arriba=0, abajo=0, Q=x

5 C=1, R=0, S=1, arriba=0, abajo=1, Q=1

10 C=1, R=0, S=0, arriba=0, abajo=0, Q=1

15 C=1, R=1, S=0, arriba=1, abajo=0, Q=0

20 C=1, R=1, S=1, arriba=1, abajo=1, Q=0

25 C=1, R=0, S=0, arriba=0, abajo=0, Q=1

30 C=1, R=1, S=1, arriba=1, abajo=1, Q=0

35 C=1, R=0, S=0, arriba=0, abajo=0, Q=0

40 C=0, R=0, S=1, arriba=0, abajo=0, Q=0

45 C=0, R=0, S=0, arriba=0, abajo=0, Q=0

50 C=0, R=1, S=0, arriba=0, abajo=0, Q=0

55 C=0, R=1, S=1, arriba=0, abajo=0, Q=0

60 C=0, R=0, S=0, arriba=0, abajo=0, Q=0

65 C=0, R=1, S=1, arriba=0, abajo=0, Q=0

70 C=0, R=0, S=0, arriba=0, abajo=0, Q=0