Jerarquía de módulos. Nombrado

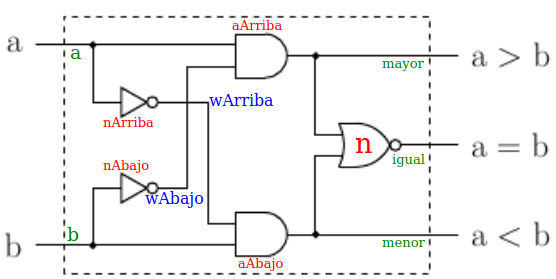

Al instanciar unos módulos dentro de otros, se forma una jerarquía de módulos. En el ejemplo del comparador de un bit de la sesión anterior, esta jerarquía de módulos se refleja en este gráfico: |

|

module TestComp1;

reg a,b;

wire M,m,igual;

Comp1 c(M,igual,m,a,b);

// Bloque de comportamiento

initial

begin

$monitor($time," a=%b, b=%b, mayor=%b, igual=%b, menor=%b",

a,b,M,igual,m);

a=0; b=0;

#5 a=0; b=1;

#5 a=1; b=0;

#5 a=1; b=1;

end

endmodule

|

// MOdulo comparador de un bit

module Comp1(output wire mayor, output wire igual, output wire menor,

input wire a, input wire b);

wire wArriba, wAbajo;

not nArriba(wArriba,a);

not nAbajo(wAbajo,b);

and aArriba(mayor,a,wAbajo);

and aAbajo(menor,b,wArriba);

nor n(igual,mayor,menor);

endmodule

|

El módulo raíz no tiene nombre y es instanciado por

Verilog automáticamente. Para hacer referencia a un objeto

directamente perteneciente al módulo raíz desde sí

mismo, simplemente se pone el nombre del objeto como ya hemos visto.

¿Pero qué hacer si queremos acceder desde el

módulo raíz a la puerta aAbajo del

módulo c? La respuesta es que se usa un

punto (.) para descender por la jerarquía de objetos.

Por consiguiente, para acceder a dicha puerta, se pondría

c.aAbajo. El esquema se generaliza cuando hay más

niveles.

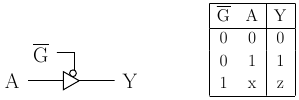

Búferes triestado

En teoría hemos visto los siguientes búferes con línea adicional de control para poder poner la salida en alta impedancia:

bufif1 bIzquierda(Y,A,G); bufif0 bDerecha(Y,A,G);También existen las equivalentes puertas NOT con control de triestado por alto y por bajo que son, respectivamente,

notif1 y notif0.

Contingencia de señales

Puede ocurrir que sobre un cable se viertan varias señales a la vez. Para que Verilog haga un tratamiento correcto de estos casos, en aquellas situaciones en que puedan coincidir varias señales, se tiene que definir la variable no comowire, sino como tri.

En el caso de contingencia en una variable de tipo

tri,

se resuelve del modo siguiente:

- Siempre tienen prioridad las señales 1, 0 ó

xfrente a las de alta impedancia (z) - Descontando las señales de alta impedancia,

si todas las señales coinciden el resultado es

ese. En caso contrario, el resultado es

x.

Algunos diseños lógicos exigen cables con funciones especiales. En caso de contingencia, actúan del siguiente modo:

tri0: igual quetri, pero si todos sonz, el valor es 0 (resistencia pull-down)tri1: ídem valor 1 (resistencia pull-up)wandotriand: basta un 0 para que el resultado sea 0worotrior: basta un 1 para que el resultado sea 1

Asignación de señales a cables

Para efectuar una conexión permanente de un registro a un cable, se debe usar una asignación. Esto hace que el valor del registro se vuelque continuamente al cable. La instrucción en verilog esassign:

wire w; reg r; assign w=r;

Ejercicio

Vamos a aplicar lo aprendido en puntos anteriores con el siguiente ejemplo de un transmisor/receptor de bus de un bit, visto en teoría:

Programemos el módulo:

module Transceiver(inout tri a, inout tri b, input wire g, input wire dir); wire ng,ndir,sa1,sa2; not (ng,g); // No hacemos referencia despuEs => no damos nombres not (ndir,dir); and (sa1,ng,dir); and (sa2,ng,ndir); bufif1 (b,a,sa1); bufif1 (a,b,sa2); endmoduleSe ha cambiado la señal G para que sea activa a nivel alto. Los nombres usados han sido:

module TestTransceiver;

tri a,b;

reg g,dir;

reg ra,rb;

Transceiver t(a,b,g,dir);

assign a=ra; assign b=rb;

// Bloque de comportamiento

initial

begin

$monitor($time," g=%b, dir=%b, a=%b, b=%b, ra=%b, rb=%b",

g,dir,a,b,ra,rb);

ra=0; rb=1; g=1; dir=0;

#5 ra='bz; rb='bz; g=1; dir=0;

#5 rb=1; g=0; dir=0;

#5 ra='bz; rb='bz; g=1; dir=1;

#5 ra=0; g=0; dir=1;

#5 ra=0; rb=1; g=0; dir=1;

end

endmodule

Observad el uso de las variables tri y la orden

assign. Antes de ejecutar la simulación,

tratad de adivinar cuáles son los valores que aparecerán

en la pantalla. ¿Qué cambios habría que hacer

para que la línea G del módulo sea activa por nivel bajo

tal y como aparecía en el diseño original?

Ejercicio

Constrúyase un módulo multiplexor 4x1 con línea de control de salida OE, de modo que si dicha línea está inactiva, la salida Y esté en alta impedancia. En caso contrario, funciona como multiplexor normal. Con dos de estos multiplexores constrúyase otro módulo multiplexor 8x1 según el esquema de la figura. Pruébese con ayuda de un módulo auxiliar.

Pista: si no sois capaces de construir el multiplexor 4x1, podéis fijaros en esta solución. Hay alternativas similares a la solución de la figura que usan un decodificador o búferes triestado, por ejemplo.

Ejercicio

Siguiendo el procedimiento descrito en teoría, y con ayuda del módulo multiplexor 8x1 construido en el ejercicio anterior, genérese la función de cuatro variables lógicas:

- Elegir una variable para cada entrada de selección. Se dará cuenta de la variable no elegida mediante las entradas D del multiplexor

- Sacar factor común de la variable no elegida en cada posibilidad de las otras

- Operar hasta conseguir que aparezcan todos los minitérminos de las variables elegidas

- Conseguimos, simplificando, que a cada línea del multiplexor hay que aplicar 0, 1, la variable no elegida o la variable no elegida negada

- Construir un módulo que imprima la tabla de verdad del diseño realizado

- Compararla con la tabla de verdad de la función h:

a b c d h 0 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0 1 1 0 0 1 0 0 0 0 1 0 1 1 0 1 1 0 0 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 0 1 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1

Órdenes de la shell relacionadas.

ls- lista el contenido de un directorio

cd- cambia el directorio de trabajo

rm- borra un fichero

man- muestra la página de manual de una orden

cat- muestra el contenido de un fichero