/* ComprobaciOn de puerta AND: TestAnd.v */

module TestAnd;

reg a,b; // Entradas

wire salida;

and a1(salida,a,b);

// Bloque de comportamiento

initial

begin

$monitor($time," a=%b, b=%b, a.b=%b", a,b,salida);

a=0; b=0;

#5 a=0; b=1;

#5 a=1; b=0;

#5 a=1; b=1;

end

endmodule |

|

En el programa definimos dos registros a y

b que van a proporcionar el valor de entrada

a la puerta y un cable salida, para obtener

la salida de la puerta según sean los valores

de a y b.

La propia puerta se crea (se instancia) a

continuación y se le da el nombre de

a1. En las puertas básicas de Verilog,

indicar un nombre es opcional. Los nombres se usan para

poder hacer referencia a los elementos creados.

En la misma línea en que

se crea la puerta, se conectan sus entradas y salidas

a las variables antes definidas.

Finalmente, viene el bloque de comportamiendo del

módulo principal TestAnd.

Damos instrucción mediante la orden

$monitor de que se sigan los cambios

de las variables a, b y

salida. Cada vez que alguna de esas variables

cambie, se imprimirá automáticamente una línea

indicando el tiempo de la simulación ($time).

Las unidades en que se mide el tiempo son arbitrarias.

A continuación,

se establece el valor inicial de a y

b a cero. Cinco unidades de tiempo

después (#5), ponemos b a

uno. Se prosigue estableciendo los otros dos casos

que quedan.

La salida del programa da el resultado esperado:

0 a=0, b=0, a.b=0

5 a=0, b=1, a.b=0

10 a=1, b=0, a.b=0

15 a=1, b=1, a.b=1

Ejercicio

Completar la tabla de la puerta AND añadiendo

como posibles entradas x (indefinido)

y z (alta impedancia). Tiene que haber,

por consiguiente, dieciséis líneas en

la tabla.

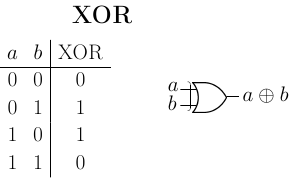

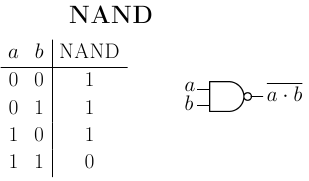

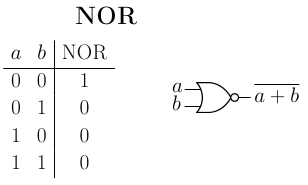

Otras puertas sencillas en Verilog

Recordemos algunas otras puertas vistas en teoría y cómo

se expresan en Verilog:

- Puerta OR,

or(salida,a,b):

- Puerta NOT,

not(salida,a):

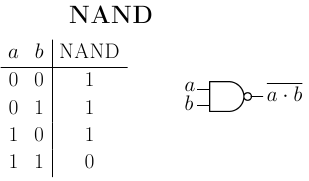

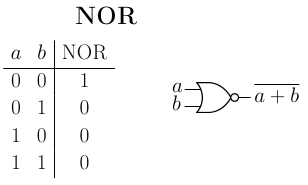

- Puertas NAND,

nand(salida,a,b),

y NOR, nor(salida,a,b):

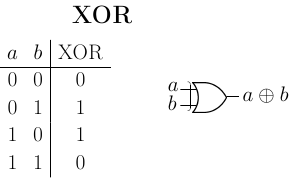

- Puertas XOR,

xor(salida,a,b),

y XNOR, xnor(salida,a,b):

- Puerta BUFFER,

buf(salida,a):

Ejercicio

Haced en un papel una tabla de dieciséis líneas y

tantas columnas como puertas lógicas vistas. Rellenad

la tabla con los valores de las puertas lógicas

correspondientes a cada posible combinación de entradas

formadas con 0,1,x y z. Añadid

una a una las puertas al código del ejercicio anterior y

comprobad con Verilog si habéis acertado al rellenar

la tabla.

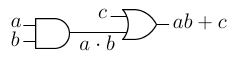

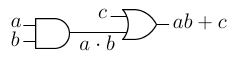

Interconexión de puertas lógicas

Vamos a construir la tabla de verdad de la función

lógica f2(a,b,c)=ab+c con la ayuda de

Verilog.

En lugar de escribir a mano los 8 casos de posibles combinaciones

de valores de a, b y c, construiremos un registro de tres

bits, le daremos valor inicial cero y lo iremos incrementando

hasta alcanzar el valor 7 (1112):

En lugar de escribir a mano los 8 casos de posibles combinaciones

de valores de a, b y c, construiremos un registro de tres

bits, le daremos valor inicial cero y lo iremos incrementando

hasta alcanzar el valor 7 (1112):

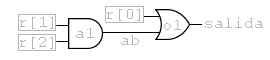

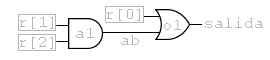

// Tabla de verdad de f2(a,b,c)=ab+c

module f2;

reg [2:0] r; // Entradas: a=r[2], b=r[1], c=r[0]

wire salida, ab;

and a1(ab,r[2],r[1]);

or o1(salida,ab,r[0]);

// Bloque de comportamiento

initial

begin

$display(" a b c | f2");

$display(" ----------");

$monitor($time," %b %b %b | %b", r[2],r[1], r[0], salida);

r=0; // r=000 => a=0, b=0, c=0

while (r!='b111) #5 r=r+1;

end

endmodule

|

| r | r[2] | r[1] | r[0] |

|---|

| 0 | 0002 | 0 | 0 | 0 |

| 1 | 0012 | 0 | 0 | 1 |

| 2 | 0102 | 0 | 1 | 0 |

| 3 | 0112 | 0 | 1 | 1 |

| 4 | 1002 | 1 | 0 | 0 |

| 5 | 1012 | 1 | 0 | 1 |

| 6 | 1102 | 1 | 1 | 0 |

| 7 | 1112 | 1 | 1 | 1 |

|

Se ha usado un cable auxiliar ab para conectar

la salida de la puerta AND a1 con una entrada

de la puerta OR o1. El resultado de su ejecución

coincide con la tabla vista en teoría:

a b c | f2

----------

0 0 0 0 | 0

5 0 0 1 | 1

10 0 1 0 | 0

15 0 1 1 | 1

20 1 0 0 | 0

25 1 0 1 | 1

30 1 1 0 | 1

35 1 1 1 | 1

|

|

Operadores relacionales

Además del ya visto !=, Verilog admite los

siguientes operadores relacionales: < (menor

que), <= (menor o igual que), ==

(igual que), >= (mayor o igual que) y

> (mayor que). Cuando alguno de los operandos

contiene x o z, el resultado es

x. En otro caso, el resultado dependerá

de si se cumple la condición (1) o no (0).

Si se desea una comparación de igualdad estricta

(considerando las xs y las zs)

se ha de usar === (estrictamente igual) y

!== (estrictamente distinto)

Operadores lógicos

Para expresar una condición dentro de un programa

Verilog, a veces es necesario disponer de los operadores

lógicos Y, O y NO. En Verilog se expresan como

&& (Y), || (O) y

! (NO). Así, para expresar algo

como: "Si no ocurre que a es mayor que cero y

b distinto de cuatro...", lo haríamos con:

if (!(a>0 && b!=4)) ...

Aplicando las leyes de De Morgan, ya sabemos que

expresamos lo mismo con:

if (a<=0 || b==4) ...

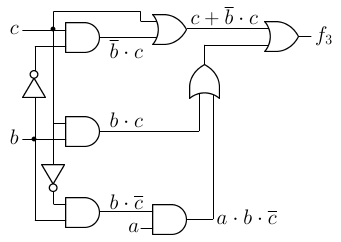

Ejercicio

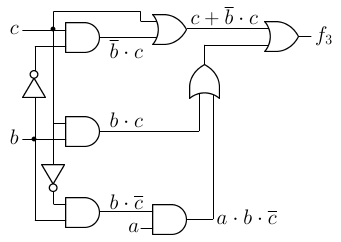

Constrúyase la tabla de verdad de la función

f3 vista en teoría y cuyo diagrama con

puertas es el que se muestra a continuación:

Ejercicio

Comprobad, mediante un programa Verilog, que la función

f3 es equivalente a esta otra elaborada

solamente con puertas NAND:

Órdenes de la shell relacionadas.

ls- lista el contenido de un directorio

cd- cambia el directorio de trabajo

rm- borra un fichero

man- muestra la página de manual de una orden

cat- muestra el contenido de un fichero

LPEs.

© 2010 Guillermo González Talaván.