Descripción a más bajo nivel

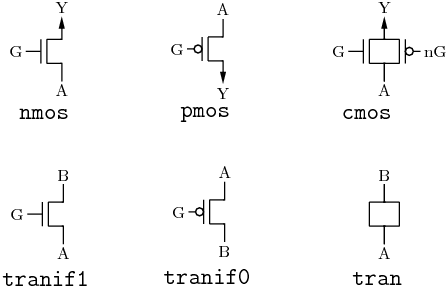

Verilog permite la descripción de un módulo basándose en puertas lógicas interconectadas o, subir de nivel, y mediante un modelo de comportamiento, describir funcionalmente las salidas y estados del módulo a partir de sus entradas.En ocasiones interesa trabajar justo en el sentido opuesto: bajar de nivel y describir el módulo en función de elementos más sencillos que las puertas. Verilog dispone de los siguientes:

- nmos(output Y, input A, input G): Y es A si G es 1, en otro caso, alta impedancia

- pmos(output Y, input A, input G): Y es A si G es 0, en otro caso, alta impedancia

- cmos(output Y, input A, input G, input nG):

es la combinación de

nmosypmos. En un funcionamiento estándar, G y nG deben ser complementarias y permiten pasar el valor de A cuando G=1 y nG=0 - tran(inout A, inout B): conecta las señales A y B (en ambas direcciones)

- tranif1(inout A, inout B, input G): conecta/aisla las señales A y B (en ambas direcciones) si G es 1/0

- tranif0(inout A, inout B, input G): conecta/aisla las señales A y B (en ambas direcciones) si G es 0/1

Los nombres de los elementos pueden llevar a engaño. Se debe tener muy en cuenta que Verilog no es un simulador electrónico y las descipciones de los elementos anteriores son meramente funcionales y físicamente inexactas. Más que transistores NMOS o PMOS, podríamos decir que son como conmutadores con las funciones descritas.

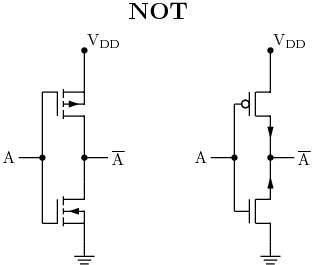

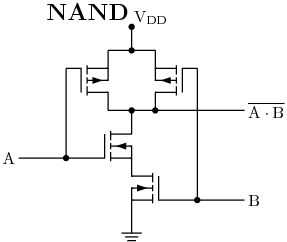

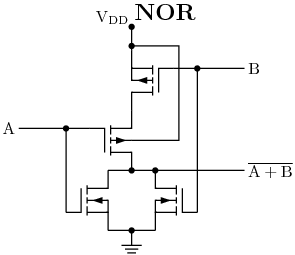

Ejercicio

Modelar mediantenmos y pmos las siguientes puertas

NOT, NAND y NOR de tecnología CMOS.

Verificar su correcto funcionamiento.

Fuerzas

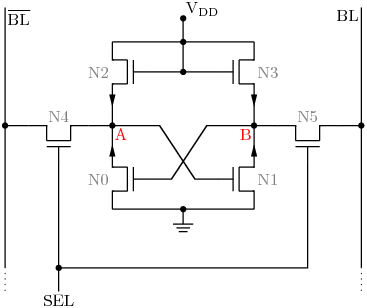

Como se acaba de comentar un poco más arriba, Verilog no es un simulador electrónico donde todas las variables físicas que intervienen en el problema (tensiones, corrientes, resitencias, etc.) son tenidas en cuenta. Prueba de ello la tenéis en el siguiente modelo de celda de memoria estática basada en tecnología NMOS:

- N4 y N5 aislan la celda del exterior. Solamente conducen en las operaciones de lectura y escritura, momento en que se activa la línea SEL de la celda

- N0 y N1 son el corazón del biestable. Los dos estados estables son A=1, B=0 y A=0, B=1. En el primero conduce N1 y en el segundo, N0.

- N2 y N3 no actúan como transistores realmente. Al tener su puerta conectada a VDD, conducen siempre. Actúan realmente como resistencias. Se hace así, porque el transistor ocupa menos que una resistencia cuando se sintetiza el circuito. Imaginemos el biestable en el estado A=1, B=0. Como N3 está conduciendo, para que B valga 0, es imprescindible que la resistencia de N3 sea mucho mayor que la resistencia de N1, de modo que la caída de tensión en N3 sea mucho mayor y, por consiguiente, la tensión en B se aproxime a 0

- Para escribir, se establece el valor que se desea en BL y su complementario y se abren N4 y N5 mediante SEL. Esto forzará al biestable a pasar al estado que le proponemos

- Para leer, se deja BL y su complementario en alta impedancia y se abren N4 y N5

Tratad de crear el módulo correspondiente en Verilog:

module CeldaSram(inout tri bl, inout tri nbl, input wire sel);Enseguida veréis que no funciona. Al no poder modelar Verilog la mayor resistencia de N2 y N3, cuando confluye un 1 y un 0 en A o B el resultado es X, cuando se debería imponer el 0. Para tratar de solucionar esto, Verilog pone a disposición del programador versiones resistivas de los elementos arriba presentados:

rnmos,

rpmos, rcmos, rtran,

rtranif1 y rtranif0.

De nuevo, se trata de una aproximación. No se tiene en cuenta el comportamiento físico exacto. Lo que hacen estos elementos es únicamente debilitar la señal que circula por ellos.

Sustituid, pues, N2 y N3 por dos rnmoses.

De este modo, casi lograréis que os funcione la celda.

Aún queda por solucionar el problema de la escritura.

El problema es similar al anterior. Se trata de forzar al biestable a que pase a un estado. Pero esto solamente es posible si la fuerza de la señal que introducimos es superior a la fuerza de las señales activas en el biestable, lo que no es el caso. Va siendo hora de que veamos las posibilidades de fuerza que tienen las señales en Verilog, de mayor a menor:

supply1 | supply0 |

strong1 | strong0 |

pull1 | pull0 |

weak1 | weak0 |

highz1 | highz0 |

Cuando confluyen dos señales en un tri, gana el

valor de la señal más fuerte. En caso de que haya

discrepancia entre las señales más fuertes, el

resultado es X. Por ejemplo, si coinciden como señales

más fuertes una pull0 con una

pull1, el resultado es pullx.

Las puertas suministran, por defecto, señales de fuerza

strong, aunque se puede especificar la fuerza,

como en este ejemplo:

buf (strong1,weak0) (salida,entrada);

También, la instrucción assign admite

especificar la fuerza con la que se asigna la señal:

assign (supply1,supply0) cable=seNal;

Los elementos vistos en esta sesión (nmos,

pmos, etc.) no admiten especificar

una señal, simplemente si transmiten una señal, la

transmiten tal cual o la atenúan, dependiendo de si son

resistivos o no.

Por todo lo visto, si queremos que nuestro biestable cambie

de estado en una escritura, necesitamos excitarlo con una

señal de fuerza supply. Para ello,

Verilog dispone de dos tipos de variable:

supply1 y supply0.

Podemos declarar variables de ese tipo que tendrán

siempre la máxima fuerza:

supply1 vdd; supply0 tierra;

También podemos atar una línea a tierra o

a 1 como si se tratara de una resistencia. La órdenes

de Verilog son pulldown y pullup.

Lo que hacen estas órdenes es verter señales

de fuerza pull. Por ejemplo, para conectar

con tierra la línea a (pulldown), la orden es:

pulldown(a);

Completad con estos datos, pues, la CeldaSram, de modo que

que se puedan hacer lecturas y escrituras.

Ejercicio

Basándose en la celda SRAM recién construida, realícese un módulo de memoria SRAM con las siguientes características:- Tamaño de la palabra: 4 bits

- Tamaño de la memoria: 16 palabras

- Señales de control: CS (selección de chip), R_W (lectura=1, escritura=0), OE (salida permitida)

- Bus de datos y bus de direcciones independientes

- Dibújese un cronograma en un ciclo de lectura y de escritura. Diseñad los tiempos de activación entre señales según os parezca oportuno

Soluciones y comentarios

Ejercicio

Construir, tomando como base ocho módulos del ejercicio anterior, un nuevo módulo de memoria SRAM con las mismas señales de control y características que el módulo del ejercicio anterior, salvo su ancho de palabra, que será 8 bits y su tamaño, que será de 64 palabras.Realizad varios ciclos de escritura y lectura para verificar su funcionamiento.

Órdenes de la shell relacionadas.

ls- lista el contenido de un directorio

cd- cambia el directorio de trabajo

rm- borra un fichero

man- muestra la página de manual de una orden

cat- muestra el contenido de un fichero